# A Novel Ten-Switch Topology for Unified Power Quality Conditioner

Abdul Mannan Rauf, Amit Vilas Sant, Vinod Khadkikar, Senior Member, IEEE and H. H. Zeineldin, Senior Member, IEEE

Abstract—This paper proposes configuration for a unified power quality conditioner (UPQC). Generally, the power structure of three-phase-three-wire UPQC consists of two back-to-back connected six switch inverters. For this configuration, out of twelve switches, six of the series inverter switches will be under-utilized most of the time. To improve the semiconductor utilization and consequently to reduce the total switch count, this paper proposes a new reduced switch topology for UPQC. The proposed topology is realized using only ten switches and retains all the performance merits of the twelve-switch UPQC while minimizing its underutilization without increasing the switch VA rating. The paper provides a detailed analytical study and evaluation by comparing the proposed topology with the twelve and nine switches based UPQC system configurations. The feasibility of the proposed topology is validated through experimental investigation.

Index Terms— Ten-switch converter, zero sequence, power quality, unified power quality conditioner (UPQC), voltage sag.

### I. INTRODUCTION

THE ever increasing use of solid state technology in industrial and domestic applications is extensively contributing towards line current harmonics, leading to nonlinear voltage drops, cables overheating, poor power factor and additional power losses at distribution levels [1]-[2]. To mitigate these problems and maintain the reliability of the delivered power within acceptable margins, stringent power quality standards are put into practice [3]. The adherence to these standards can be achieved with a custom power device such as the unified power quality conditioner (UPQC) [4]-[8]. Being a versatile and flexible power electronic device, UPQC has become the most attractive solution to power quality problems at the distribution level [9].

A UPQC generally consists of two voltage source inverters

Manuscript received June 11, 2015; revised Oct 15, 2015; accepted Dec 04, 2015.

(VSI), connected in shunt and series configuration with the

grid, at the point of common coupling (PCC) and share a common dc link capacitor [4]. The series VSI protects the downstream loads from sags/swells in the PCC voltage whereas the shunt VSI reduces the upstream line losses by compensating the harmonic distortion and reactive component of the load current. When the voltage at PCC is distorted, the series VSI can be additionally controlled to mitigate and prevent the voltage harmonics from reaching the load [10]. There is an extensive literature available on UPQC and a detailed review can be found in [4].

Although back-to-back UPQC with twelve switches offers independent control of both VSIs and excellent mitigation of grid disturbances, its series VSI is generally underutilized. During normal conditions the series VSI (six out of twelve switches) remain either completely inactive or operate at very low modulation index. This under-utilization of the series VSI may give rise to computational problems as addressed in [11]-[12].

This paper proposes a new reduced switch UPQC system topology that comprises of ten switches in total. The main objective is to reduce the overall switch count of the back-to-back UPQC system while retaining its operational features without any performance tradeoff. To maintain the linear modulation range and uniform switching frequency for all the switches within the proposed topology, a carrier based double zero sequence injection scheme is also developed. An appropriate control algorithm is developed to achieve the seamless operation of the proposed UPQC topology under different operating conditions. An experimental study is carried out to validate the performance of the proposed topology.

# II. THREE PHASE THREE WIRE UPQC SYSTEM CONFIGURATIONS

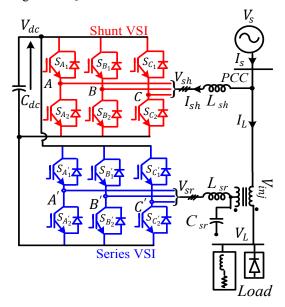

For three-phase-three-wire system, generally, the back-to-back inverter based UPQC system is widely used and is shown in Fig. 1. It comprises of twelve power semiconductor switches in total. Switches  $\{S_{A1}, S_{B1}, S_{C1}, S_{A2}, S_{B2}, S_{C2}\}$  constitute the shunt VSI which is connected at the PCC, whereas, the switches  $\{S_{A1'}, S_{B1'}, S_{C1'}, S_{A2'}, S_{B2'}, S_{C2'}\}$  constitute the series VSI and is connected between the PCC and load. Both inverters share the common dc link capacitor. As shown in Fig. 1, the twelve-switch UPQC deploys two dedicated inverters for

Copyright (c) 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permission@ieee.org.

A. M. Rauf, and V. Khadkikar are with the Department of Electrical Engineering and Computer Science, Masdar Institute, Abu Dhabi, United Arab Emirates (email: arauf@masdar.ac.ae).

H. H. Zeineldin is with the Department of Electrical Engineering and Computer Science, Masdar Institute, Abu Dhabi, UAE, and is currently on leave from the Faculty of Engineering, Cairo University, Giza, 12316, Egypt.

performing the UPQC functionalities.

Fig. 1. Twelve-switch UPQC topology.

This feature allows UPQC to have shunt VSI connected at either the PCC or load with no effect on the compensation ability.

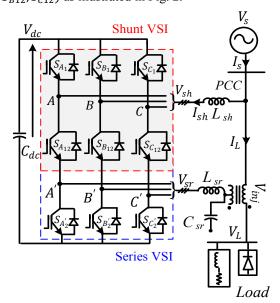

Recently, there has been an effort to reduce the total switch count of the UPQC as reported in [13]. By merging the lower three switches of the shunt VSI  $\{S_{A2}, S_{B2}, S_{C2}\}$  and upper three switches of the series VSI  $\{S_{A1'}, S_{B1'}, S_{C1'}\}$  in Fig. 1, the reduced nine-switch UPQC topology is achieved in [13]. This configuration has a set of three shared switches  $(S_{A12}, S_{B12}, S_{C12})$  as illustrated in Fig. 2.

Fig. 2. Nine-switch UPQC topology.

The configuration features saving of three switches and performs satisfactorily under normal and sag conditions without an increase in the dc link voltage. However, it causes considerable rise in the switch current ratings of two switches per phase which is mainly attributed to the series connection of three switches in each leg (discussed in Section-IV). Therefore, six out of nine switches must be oversized for adequate operation of the nine-switch UPQC. In addition, all the nine switches must remain operational irrespective of the UPQC compensation mode. Thus, the reliability of the nine-switch UPQC reduces for a single switch malfunction.

#### III. PROPOSED TEN-SWITCH UPQC TOPOLOGY

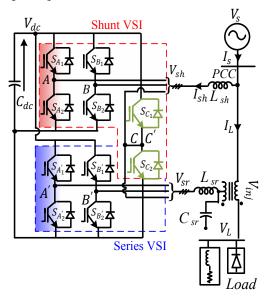

In this paper, a new topology of UPQC, based on ten switches, is proposed for power quality enhancement applications. As depicted in Fig. 3, the proposed topology is realized by combining the phase C switches of shunt and series VSI  $\{S_{C1}, S_{C2}\}$  and  $\{S_{C1'}, S_{C2'}\}$  in Fig. 1, respectively, into a common leg with a shared set of two switches  $S_{C1}$  and  $S_{C2}$ . Until now the ten-switch structure has been utilized in drives applications with certain limitations. The following subsection provides an overview of the ten-switch related work in the literature [14-21].

Fig. 3. Proposed ten-switch UPOC topology.

# A. Existing constraints and background work related to tenswitch structure

Like most reduced semiconductor topologies, ten-switch structure faces restriction on its allowable switching states for the shared leg (phase C in Fig. 3). Table I and II reflects various switching states for the twelve and ten-switch configurations, respectively. It can be clearly seen from Table II that the output terminals for the shared leg "C" can be connected to either  $V_{dc}$  or ground. Unlike the back-to-back configuration, the switching state where the upper terminal is connected to  $V_{dc}$  and lower terminal is connected to ground (i.e.  $V_{sh} = V_{dc}$  and  $V_{sr} = 0$ ) or vice-versa is not realizable as it will result in a direct short circuit of the dc bus. The blocking of two (out of four) states limits the dc link voltage available for the shared leg ("phase C") to half of its value for back-to-back configuration.

TABLE I SWITCHING STATES FOR PHASE "C" OF SHUNT AND SERIES VSI IN TWELVE-SWITCH CONFIGURATION

| Voltage                            | Switching State                                                 |  |  |  |  |  |

|------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

| $V_{sh} = V_{sr} = V_{dc}$         | $S_{C1}, S_{C'1} = \text{ON and } S_{C2}, S_{C'2} = \text{OFF}$ |  |  |  |  |  |

| $V_{sh} = V_{sr} = 0$              | $S_{C2}$ , $S_{C'2}$ = ON and $S_{C1}$ , $S_{C'1}$ = OFF        |  |  |  |  |  |

| $V_{sh} = V_{dc}$ and $V_{sr} = 0$ | $S_{C1}$ , $S_{C'2}$ = ON and $S_{C2}$ , $S_{C'1}$ = OFF        |  |  |  |  |  |

| $V_{sh} = 0$ and $V_{sr} = V_{dc}$ | $S_{C2}$ , $S_{C'1}$ = ON and $S_{C2}$ , $S_{C'1}$ = OFF        |  |  |  |  |  |

TABLE II

SWITCHING STATES FOR PHASE "C" OF SHUNT AND SERIES VSI IN

TEN-SWITCH CONFIGURATION

| Voltage                            | Switching State                                       |  |  |  |  |

|------------------------------------|-------------------------------------------------------|--|--|--|--|

| $V_{sh} = V_{sr} = V_{dc}$         | $S_{C1}$ = ON and $S_{C2}$ = OFF                      |  |  |  |  |

| $V_{sh} = V_{sr} = 0$              | $S_{C1} = \text{OFF} \text{ and } S_{C2} = \text{ON}$ |  |  |  |  |

| $V_{sh} = V_{dc}$ and $V_{sr} = 0$ | Not Realizable                                        |  |  |  |  |

| $V_{sh} = 0$ and $V_{sr} = V_{dc}$ | Not Realizable                                        |  |  |  |  |

Ten-switch configuration was earlier reported in [14]-[16] to replace twelve-switch back-to-back converter for dual induction machine drive system. Although the configuration allows independent control of both machines with a wide range of variation in load torque and rotational speeds, it imposes a limitation on the dc link voltage. If  $U_{m1}$  and  $U_{m2}$  are the maximum values of phase-to- phase voltages at the terminals of the induction machine  $M_1$  and  $M_2$ , respectively, it is shown in [17] that,

Where  $V_{DC}$  is the voltage across the dc link capacitor. In the special case of  $U_{m1} = U_{m2} = U$  the following constraints can be established.

$$V_{DC} \ge 2U \quad for \ ten - switch \ system$$

$V_{DC} \ge U \quad for \ twelve - switch \ system$  (2)

Equation (2) implies that the dc link voltage must be doubled to achieve the maximum rotational speed for both machines simultaneously. Doubling of dc link voltage increases all the component stress by two folds, thus, offsetting the saving of two switches. For the same dc link voltage, the ten-switch structure leads to reduction in the terminal voltage and consequent speed range of both machines.

Attempts to enhance the dc-bus utilization for the ten-switch architecture have been reported in [18]-[21]. The improvement reported, in [18], is obtained at the expense of identical operating (speeding and loading) conditions for both machines. In [19], the controller divides the dc link voltage by allocating predefined switching vectors to each machine. The restriction that the controller must have prior knowledge of the voltage

profile for each machine makes the scheme impractical for variable industrial loads. In [20], the ten-switch configuration is employed to drive the two induction motors in the center driven winders. It overcomes the limitation of dc link oversizing given by (1)-(2) due to 'inverse loading profile" of the two machines. When one motor operates at maximum speed, the other motor operates at minimum speed and vice versa. Since both motors increase/decrease speed in an alternate fashion, their voltage requirement is completely different (opposite). This allows the ten-switch system to remain operational for center driven winders utilizing the same dc link voltage required for back-to-back converter. However, the center driven winder is a special case and in general ten-switch configuration have not shown much economic value for dual motor drive systems.

#### B. Proposal

This paper proposes the use of ten-switch configuration as the most suitable candidate for shunt-series configuration, such as, UPQC. The rationale behind this recommendation is given below.

As shown in Fig. 3, the outputs of the upper VSI are connected to the PCC constituting the shunt configuration, whereas, the outputs of lower VSI are connected in series with the same PCC constituting the series configuration. The shared set of switches  $S_{C1}$  and  $S_{C2}$  are driven by the modulation signal which is calculated as follows.

$$m_{res} = m_{sh} + m_{sr} \tag{3}$$

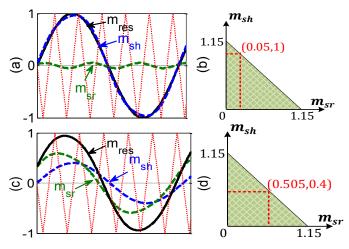

Where  $m_{sh}$  and  $m_{sr}$  are the amplitude of the modulating signal for shunt and series VSIs, respectively.  $m_{res}$  is the resultant modulating signal for the shared set of switches. Fig. 4(a) shows these details within the bandwidth of the dc link voltage in per unit (p.u) where  $\{1,0,-1\}$  corresponds to  $\{V_{dc},0,-V_{dc}\}$ . To maintain the linear range of modulation for  $S_{C1}$  and  $S_{C2}$ , the maximum allowable limit for  $m_{res}$  is -1 to +1. This limit can be further stretched by 15% using third harmonic injection [11]-[12] extending the linear range from  $\{-1,1\}$  to  $\{-1.15,1.15\}$  as shown in Fig. 4(b) and 4(d). Thus, up to 15% THD in the PCC voltage can be compensated without increasing the dc-link voltage. For higher values of voltage THD, (i.e.> 15%), like all existing configurations, the proposed topology will also require a higher dc-link voltage. During normal condition, the shunt VSI supplies harmonic and

fundamental reactive component of the load current while the series VSI injects the inverse of PCC voltage harmonics usually < 5% [11]. Since the shunt VSI operates at the same voltage level as PCC (1 p.u.), its reference signal amplitude is also unity. From (3), the amplitude of the reference signal for shared leg can go as high as 1.05 as shown in Fig. 4(a). If an ideal grid is considered (with no distortion in PCC voltage) the series VSI will simply operate with a modulation index of zero and  $m_{res} = m_{sh} = 1$ .

Now consider that there is sag of magnitude  $\Delta V_{sag}$  (p.u) in the PCC voltage. On the occurrence of sag, the PCC voltage undergoes a reduction of  $\Delta V_{sag}$ . The shunt VSI modulation

index also decreases proportionally to the new value of  $(1 - \Delta V_{sag})$ . The series VSI compensates the sag by injecting a fundamental voltage given by

$$V_{sr} = V_L^* - V_{pcc} \tag{4}$$

Where  $V_L^*$  is the nominal load voltage. The new modulation index of the series VSI increases from 0.05 to  $\Delta V_{sag} + 0.05$ . Fig. 4(c) reflects the transition in all three modulation indexes  $\{m_{sr}, m_{sh}, m_{res}\}$  from normal to sag mode of operation.

It can be observed from Figs. 4(a) and 4(c) that the resultant modulation signal for the shared leg (phase "C") does not extend out of the dc-link bandwidth during both (normal and sag) modes of operation. This is attributed to the fact that amplification in  $m_{Sr}$  by any amount is always accompanied by a reduction in  $m_{Sh}$  by the same factor. The self-tuning feature of both the modulation references causes the shared leg switches to always operate in the linear range of modulation. Thus, the proposal of the utilization of a ten-switch topology for UPQC can be concluded as the most suitable application. Figs. 4(b) and 4(d) reflect the operational area of the tenswitch UPQC for normal and sag mode of operations, respectively. The operating points  $\{0.05,1\}$  in Fig. 4(b) and  $\{0.505,0.4\}$  in Fig. 4(d) correspond to the normal mode in Fig. 4(a) and sag mode in Fig. 4(c), respectively.

Fig. 4 Modulation references transition for shared leg during normal (upper) and sag (lower) mode of operation in proposed configuration.

# IV. SWITCH RATING ANALYSIS

In section III, a subjective explanation is presented to use ten-switch configuration as UPQC. Despite its two switch saving feature, the effectiveness of the proposed ten-switch UPQC can only be evaluated after comprehensive analysis of its switch rating. Therefore, an analytical study is presented in this section to determine and compare the switch rating of the ten-switch UPQC with the twelve and nine-switch topologies.

From Fig. 1, the per unit current flowing in the series and shunt VSI can be expressed as

$$i_{Sr} = \frac{i_L \angle \theta_{La}}{n_t} = \sum_{h=1}^{\infty} I_L \cos(hw_L t + \varphi_{Lh}) = I_L \angle \theta_L = 1 \angle \theta_L$$

$$i_{Sh} = \sum_{h=1}^{\infty} I_{Sh} \cos(hw_{Sh} t + \varphi_{Sh-h}) = (1 \angle \theta_L - 1 \cos \theta_L) + I_{1K}$$

(5)

Where h=1, 2, 3 is the harmonic order,  $i_{sr}$  and  $i_{sh}$  are the terminal currents of series and shunt VSIs, respectively. Considering the load current magnitude as the base and angle of the fundamental PCC voltage as the reference angle, transformer turns ratio  $n_t$  as unity, the series VSI current  $i_{sr}$  is 1p.u as shown in the first part of (5). The shunt VSI current  $i_{sh}$ consists of fundamental reactive and harmonic portion of load current. In the second part of (5),  $\cos \theta_L$  denotes the fundamental active component of load current whereas  $I_{1K}$ accounts for the additional fundamental active component required to maintain the dc-link voltage. During steady state,  $I_{1K}$  represents the loss component of the UPQC system and during sag condition, it also contains the active power component to achieve the overall power balance [7]. For simplicity, neglecting the inverter losses and defining the sag depth as  $k = 1 - V_L$ . The current  $I_{1K}$  can be expressed as,

$$I_{1K} = \begin{cases} 0 & if \quad k = 0\\ \left(\frac{1}{1 - k}\right) \cos \theta_L & if \quad 0 \le k \le 1 \end{cases}$$

(6)

From (6) it is clear that  $I_{1K}$  is a function of the load power factor and sag depth during off nominal conditions. Furthermore, it can be observed from (5) that  $i_{Sr}$  and  $i_{Sh}$  have different magnitudes and phase angles.

## A. Switch rating of back-to-back UPQC

Using the derivations given in [22], the switch current for the back-to-back UPQC of Fig. 1 can be expressed as.

$$i_{SA_{1}} = \sum_{\sigma=1 \to fsw} \{2(k_{1})(T - T_{1})i_{sh}\}_{\sigma}$$

$$i_{SA'_{1}} = \sum_{\sigma=1 \to fsw} \{2(k_{2})(T_{2})i_{sr}\}_{\sigma}$$

$$k_{1} = \begin{cases} 1, & i_{sh} \leq 0 \\ 0, & > 0 \end{cases}$$

$$k_{2} = \begin{cases} 1, & i_{sr} \leq 0 \\ 0, & i_{sr} > 0 \end{cases}$$

$$(7)$$

Where  $i_{SA_1}$  and  $i_{SA_1'}$  are phase A switch currents of shunt and series VSIs, respectively. T is the half switching period of the carrier waveform.  $T_1$  is the time interval during which the amplitude of carrier is higher than the modulating signal  $SA_1$  amplitude.  $T_2$  is the time interval during which the amplitude of modulating signal  $SA_1'$  is higher than the carrier.  $k_1$  and  $k_2$  are symbolic variables governing the unidirectional current through  $SA_1$  and  $SA_1'$ . Based on (7), the maximum current rating of each switch in series VSI is  $1 \angle \theta_L$  (p.u) and shunt VSI is  $(1 \angle \theta_L - 1\cos \theta_L) + I_{1K}$  (p.u). The voltage rating of each switch in the twelve-switch converter is same as the dc link voltage. Considering the nominal rms load voltage (1 p. u) as base, the dc link voltage would be  $2\sqrt{2}$  (p.u).

#### B. Switch rating of nine-switch UPQC

In the nine-switch UPQC topology of Fig. 2, the switch current can be expressed as follows [22]-[23].

$$i_{SA_{1}} = \sum_{\sigma=1 \to f_{SW}} { 2(k_{1})(T - T_{1} - T_{2})i_{sh} + \choose (k_{3})T_{2}(i_{sh} + i_{sr}) }_{\sigma}$$

$$i_{SA_{12}} = \sum_{\sigma=1 \to f_{SW}} { 2(1 - k_{1})(T_{1})i_{sh} + \choose (k_{2})T_{2}i_{sr} }_{\sigma}$$

$$i_{SA_{2}} = \sum_{\sigma=1 \to f_{SW}} { 2(1 - k_{2})(T - T_{1} - T_{2})i_{sr} + \choose (1 - k_{3})T_{1}(i_{sh} + i_{sr}) }_{\sigma}$$

$$k_{1} = \begin{cases} 1, & i_{sh} \leq 0 \\ 0, & > 0 \end{cases} k_{2} = \begin{cases} 1, & i_{sr} \leq 0 \\ 0, & i_{sr} > 0 \end{cases} k_{3} = \begin{cases} 1, i_{sh} + i_{sr} \leq 0 \\ 0, i_{sh} + i_{sr} > 0 \end{cases}$$

$$(8)$$

Based on (8) and the derivation in [23], the maximum current handled by three upper switches of the shunt VSI  $\{S_{A1}, S_{B1}, S_{C1}\}$  and three lower switches of the series VSI  $\{S_{A2'}, S_{B2'}, S_{C2'}\}$  is  $(2 \angle \theta_L - \cos \theta_L) + I_{1K}$  (p.u). The current rating of the shared set of switches will be  $max\ of\ (i_{sh}, i_{sr})$ . The voltage rating of all the switches is  $2\sqrt{2}$  (p.u.) similar to the twelve-switch UPQC. Further explanation on nine-switch converter rating and loss analysis can be found in [22]-[23].

#### C. Switch rating of proposed ten-switch UPQC

The instantaneous current for the shared set of switches  $SC_1$  and  $SC_2$  in the proposed ten-switch UPQC of Fig. 3 can be expressed as follows.

$$i_{SC_{1}} = \sum_{\sigma=1 \to f_{SW}} \{2(k_{1})(T_{1})i_{sh}\}_{\sigma}$$

$$i_{SC_{2}} = \sum_{\sigma=1 \to f_{SW}} \{2(k_{2})(T_{2})i_{sr}\}_{\sigma}$$

$$k_{1} = \begin{cases} 1, & i_{sh} \geq 0 \\ 0, & < 0 \end{cases}$$

$$k_{2} = \begin{cases} 1, & i_{sr} \leq 0 \\ 0, & i_{sr} > 0 \end{cases}$$

(9)

The current rating of the above two shared set of switches will be max of  $(i_{sh}, i_{sr})$ . The remaining four shunt VSI switch currents and four series VSI currents are identical to that of the twelve-switch shunt and series VSIs, respectively. Similar to nine-switch topology, the voltage rating of all the switches is  $2\sqrt{2}$  p.u.

## D. Comparative Analysis

Using the aforementioned expressions for the currents and dc-link voltage requirements, a comparative switch rating analysis is conducted for the three UPQC topologies. Table III provides a summary of the comparison. It can be clearly seen that the total VA rating of the nine-switch UPQC is higher than twelve-switch topology by a factor of 3Y. Since the maximum value of Y is always less than X [i.e.  $max(i_{sh},i_{sr}) < (i_{sh} + i_{sr})$ ], the total VA rating of the proposed UPQC topology will always be lower than the twelve-switch topology.

For a better illustration, an analytical comparison of VA loading for the three UPQC topologies is conducted and given in Table IV. The sag depths of 0.2, 0.4 and 0.6 are considered with a linear inductive load of  $1\angle -30^{\circ}$ . It can be seen from Table IV that among all three topologies nine-switch topology requires highest VA loading whereas the proposed topology performs the same tasks with the least VA loading of the UPOC system.

For example, for a sag depth of 0.6 p.u, it can be observed that compared with the twelve-switch topology the proposed topology, in addition to saving of two semiconductor switches, requires 2% less VA whereas the nine-switch topology needs at least 60% higher VA loading

TABLE III

PER UNIT COMPONENT RATING OF SEMICONDUCTORS AND OVERALL VA RATING FOR VARIOUS UPQC TOPOLOGIES

| UPOC No Maxim                                     |    |                                    | Maximum                                        | Switch Current Ratin                        |                        |                                                                                                                                                             |  |

|---------------------------------------------------|----|------------------------------------|------------------------------------------------|---------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TOPOLOGY   Of switches   Voltage Rating   Shunt V |    | Dedicated<br>Shunt VSI<br>switches | Dedicated Series VSI<br>switches               | Shared<br>switches                          | Overall UPQC VA Rating |                                                                                                                                                             |  |

| Twelve-switch                                     | 12 | $2\sqrt{2}$                        | $(1\angle\theta_L - \cos\theta_L) + I_{1K}$    | $1 \angle \theta_L$                         | _                      | $VA = 6X$ $X = 2\sqrt{2} ((2\angle \theta_L - \cos \theta_L \angle 0) + I_{1K})$                                                                            |  |

| Nine-switch                                       | 9  | $2\sqrt{2}$                        | $(2\angle\theta_L - \cos\theta_L) + I_{1K}$    | $(2\angle\theta_L - \cos\theta_L) + I_{1K}$ | $max(i_{sh,}i_{sr})$   | $VA = 6X + 3Y$ $X = 2\sqrt{2} \left( (2\angle \theta_L - \cos \theta_L) + I_{1K} \right)$ $Y = 2\sqrt{2} \left( max \left( i_{sh,} i_{sr} \right) \right)$  |  |

| Proposed Tenswitch                                | 10 | 2√2                                | $(1 \angle \theta_L - \cos \theta_L) + I_{1K}$ | $1 \angle 	heta_L$                          | $max(i_{sh},i_{sr})$   | $VA = 4X + 2Y$ $X = 2\sqrt{2} \left( (2\angle \theta_L - \cos \theta_L) + I_{1K} \right)$ $Y = 2\sqrt{2} \left( max \left( i_{sh,i} i_{sr} \right) \right)$ |  |

| TABLE IV                                           |

|----------------------------------------------------|

| PER UNIT VA LOADING OF UPOC FOR VARIOUS SAG DEPTHS |

| SAG DEPTH                            |      | Normal conditions |       | 0.2  |      | 0.4   |      |      | 0.6   |      |      |       |

|--------------------------------------|------|-------------------|-------|------|------|-------|------|------|-------|------|------|-------|

| UPQC TOPOLOGY                        | X    | Y                 | total | X    | Y    | total | X    | Y    | total | X    | Y    | total |

| Twelve-switch $(VA = 6X)$            | 3.74 | -                 | 22.45 | 6.19 | -    | 37.16 | 7.12 | -    | 42.75 | 9.03 | -    | 54.17 |

| Nine-switch UPQC ( $VA = 6X + 3Y$ )  | 3.74 | 2.8               | 30.9  | 6.19 | 5.68 | 54.1  | 7.12 | 6.68 | 62.76 | 9.03 | 8.69 | 80.23 |

| Proposed Ten-switch $(VA = 4X + 2Y)$ | 3.74 | 2.8               | 20.62 | 6.19 | 5.68 | 36.2  | 7.12 | 6.68 | 41.84 | 9.03 | 8.69 | 53.48 |

#### V. MODULATION SCHEME FOR TEN-SWITCH UPQC

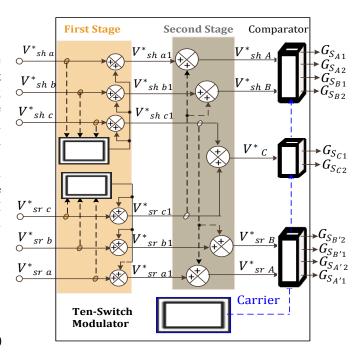

Fig. 5 shows the developed modulation scheme to generate gate pulses for the proposed ten-switch UPQC topology. It involves dual stage zero sequence injection in the modulating references. The inputs to the modulator block are three reference signals each from the shunt and series VSI control blocks (further explained in section VI). The developed modulation technique has two stages that are explained below. In the first stage, to enhance the dc bus utilization, the third harmonic injection is carried out. Let,  $V_{sh\ a,b,c}^*$  and  $V_{sr\ a,b,c}^*$  be the reference signals determined by the shunt and series VSI control blocks, respectively. These signals can be represented as,

$$V_{Sh-a}^{*} = M_{Sh} \cos(w_{Sh}t + \emptyset_{Sh}) V_{Sh-b}^{*} = M_{Sh} \cos(w_{Sh}t - 120^{o} + \emptyset_{Sh}) V_{Sh-c}^{*} = M_{Sh} \cos(w_{Sh}t - 240^{o} + \emptyset_{Sh})$$

$$(10)$$

$$V_{sr-a}^* = M_{sr} \cos(w_{sr}t + \emptyset_{sr})$$

$$V_{sr-b}^* = M_{sr} \cos(w_{sr}t - 120^o + \emptyset_{sr})$$

$$V_{sr-c}^* = M_{sr} \cos(w_{sr}t - 240^o + \emptyset_{sr})$$

$$(11)$$

Where,  $M_{sh}$ ,  $w_{sh}$ , and  $\emptyset_{sh}$  are the modulation ratio, angular frequency, and phase angle of the shunt VSI.  $M_{sr}$ ,  $w_{sr}$ , and  $\emptyset_{sr}$  are the corresponding values for the series VSI, respectively. Using the third harmonic injection method [11], the zero sequence signal can be obtained as,

$$V_{no-sh} = -0.5 \cdot \left[ Max(V_{sh\,a,b,c}^*) + Min(V_{sh\,a,b,c}^*) \right]$$

(12)

$$V_{no-sr} = -0.5 \cdot \left[ Max \left( V_{sr\;a,b,c}^* \right) + Min \left( V_{sr\;a,b,c}^* \right) \right] \tag{13}$$

Where,

$$V_{sh-i1}^* = V_{sh-i}^* + V_{no-sh} \tag{14}$$

$$V_{sr-i1}^* = V_{sr-i}^* + V_{no-sr}$$

(15)

and  $V_{sh-i}^*$  and  $V_{sr-i}^*$  (i=a,b,c) represent the three modified sinusoidal reference signals for shunt and series VSIs, respectively.

Fig. 5. Modulation scheme for the proposed ten-switch UPQC system.

In the second stage, five modulating signals for each leg, from the six aforementioned references, are generated. The series VSI reference for the shared phase "C" is added to the three modified shunt VSI references of (14). Similarly, the shunt VSI reference for the shared phase "C" is added to the three modified series VSI references of (15). The resulting signals, are expressed as,

$$\begin{vmatrix} V_{sr-A}^* = V_{sr-a1}^* + V_{sh-c1}^* \\ V_{sr-B}^* = V_{sr-b1}^* + V_{sh-c1}^* \\ V_C^* = V_{sr-c1}^* + V_{sh-c1}^* \\ V_{sh-A}^* = V_{sh-a1}^* + V_{sr-c1}^* \\ V_{sh-B}^* = V_{sh-b1}^* + V_{sr-c1}^* \end{vmatrix}$$

(16)

In (16),  $V_{sr-c1}^*$  is added to  $V_{sh-a1}^*$ ,  $V_{sh-b1}^*$ ,  $V_{sh-c1}^*$ , and  $V_{sh-c1}^*$  is added to  $V_{sr-a1}^*$ ,  $V_{sr-b1}^*$ , and  $V_{sr-c1}^*$ . This addition does not affect the reference modulation signals of shunt and series VSIs as the added signals  $V_{sr-c1}^*$  and  $V_{sh-c1}^*$  only appear as zero-sequence components and cancel out in line-to-line voltages at the ac terminals of shunt and series VSIs,

respectively. Therefore, five modulating signals are generated out of six reference signals at the output of the second stage as shown in Fig. 5. The comparators then generate the required gate signals for the ten switches.

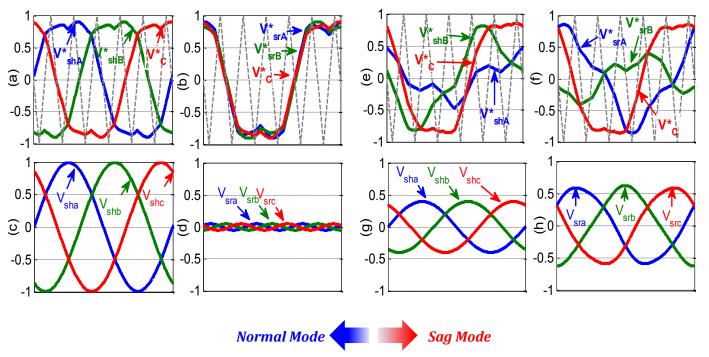

To illustrate the performance of the proposed ten-switch topology, a scenario is considered where linear RL Load is connected to a distorted supply voltage having THD < 5% and the fundamental voltage magnitude of 1p.u. In this case, the shunt VSI requires the maximum dc-link voltage for load reactive power compensation. This infers that the peak modulation magnitudes the shunt reference of indices( $V_{sh-ABC}^*$ ) in (16) would be very close to unity which is given in Fig. 6(a). The corresponding output voltages at the shunt VSI terminal are shown in Fig. 6(c). However, as shown in Fig. 6(b), the reference modulation indices for series VSI  $(V_{sr-ABC}^*)$  have peak magnitudes of approximately unity due to the addition of common phase "C" modulation index in stage-2. Nevertheless the effective contribution of these reference signals towards the injected voltage will correspond to only a small voltage as shown in Fig. 6(d) consisting of the voltage required to compensate the harmonics in the PCC voltage. This is due to the fact that the added zero sequence signals effectively cancel out in the injected line-line voltages.

When there is a drop in the PCC voltage, the peak amplitude of the voltage at shunt VSI terminals decreases as shown in Fig. 6(g). To compensate the sag, the output voltage amplitude of the series VSI increases. Figs. 6(f) and (h) reflect the transition in series VSI reference and output voltage during sag condition.

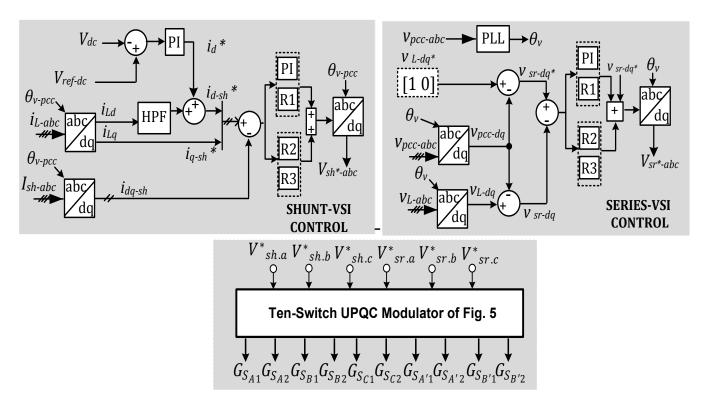

# VI. CONTROL SCHEME FOR THE PROPOSED TEN-SWITCH UPQC

#### A. Control for Shunt-VSI

The task of the shunt VSI is to compensate the reactive and harmonic components of load current and regulate the dc link voltage during normal and sag conditions. To realize these objectives, the control scheme is shown in Fig. 7. The measured load current  $i_{L\ abc}$  is converted to the synchronous reference frame quantitates  $i_{L\ d}$  and  $i_{L\ q}$  which are given as.

$$i_{Ld} = \bar{\iota}_{Ld} + \tilde{\iota}_{Ld} i_{Lq} = \bar{\iota}_{Lq} + \tilde{\iota}_{Lq}$$

$$(17)$$

where  $\bar{\iota}_{L\,d}$  and  $\bar{\iota}_{L\,q}$  correspond to the fundamental active and reactive components of load current, respectively.  $\tilde{\iota}_{L\,d}$  and  $\tilde{\iota}_{L\,q}$  reflect the harmonic components of  $i_L$ . The reference current of the shunt VSI can be expressed as

$$i_{ref-sh} = \tilde{i}_{Ld} + i_{Lg} + i_{Loss} \tag{18}$$

where  $\tilde{\imath}_{L\,d}$  is obtained by passing  $i_{L\,d}$  through a high-pass filter.  $i_{Loss}$  corresponds to the active component of the source current required to maintain the dc link voltage at rated value.  $i_{ref-sh}$  is compared with actual shunt current  $i_{sh}$  in the synchronous frame and the error is processed through a combination of proportional-integral (PI) and set of resonant R) controllers to track the reference value. The resulting output signals are transformed back to the stationary reference frame giving  $V_{sh\ a,b,c}^*$  constituting the reference modulating signals for the shunt VSI.

Fig. 6 Representation of modulation indexes and output voltages after second stage for (a),(c) shunt VSI during normal mode (b),(d) series VSI during normal mode (e),(g) shunt VSI during sag mode and (f),(h) series VSI during sag mode.

Fig. 7. Detailed control block diagram for the proposed ten-switch UPQC

## B. Control for Series-VSI

The objective of the series VSI is to maintain the rated sinusoidal voltage at load terminals regardless of the voltage variation at the PCC. The overall series VSI control block is shown in Fig. 7.

The difference between the series VSI reference voltage  $(V_{sr-vsi-dq}^* = V_{L-dq}^* - V_{pcc-dq})$  and actual voltage  $(V_{sr-vsi-dq} = V_{L-dq} - V_{pcc-dq})$  is processed by a combination of PI and resonant controllers in the synchronous reference frame. For sag detection the absolute error between PCC reference voltage (1 p.u.) and the actual PCC voltage magnitude (p.u.) in the synchronous reference frame is calculated as follows.

$$V_{error} = \left| 1 - \sqrt{V_{pcc-d}^2 - V_{pcc-q}^2} \right| \tag{19}$$

The controller continuously monitors  $V_{error}$  and as soon as it exceeds the threshold of zero p.u., sag is detected. Although  $V_{sr-vsi-dq}^*$  can be directly used to control the series VSI in open loop by converting it into the stationary reference frame however it will not be able to compensate the drop across VSI switches, interfacing filter and series transformer. It is therefore added as a feed forward signal to the output of PI to compensate for system losses. The resulting signal is converted into the stationary frame giving  $V_{sr-vsi\ a,b,c}^*$  which is the reference modulating signal for series VSI.

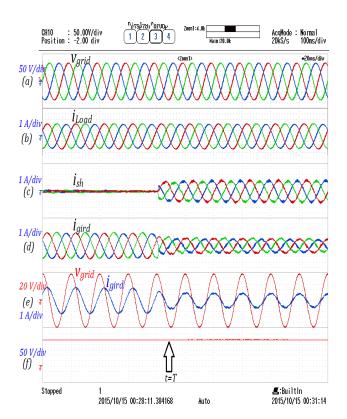

#### VII. EXPERIMENTAL STUDY

To validate the performance of the proposed ten-switch UPQC, an experimental prototype is developed. A digital

signal processor (DSP), dSPACE DS1103, is used to control the shunt and series inverters of the ten-switch UPQC. The developed algorithm requires a sampling time of  $50~\mu s$  to execute the code on dSPACE DS1103. Both inverters operate at a switching frequency of 10 kHz. To emulate the sag and harmonic distortion in the grid voltage, a three phase programmable source is used. The experimental system parameters are listed in Table V. Note that in all the experimental results the PCC and load voltages are shown as line to line voltages, whereas, the series injected voltages are shown as phase voltages across series transformer).

$\label{eq:table_v} TABLE\;V$  UPQC system data for experimental study

| Programmable voltage source | Supply voltage: 175 $V_{L-L\ peak}$ , 50 Hz<br>Source Impedance: $R_g = 0.047\ \Omega$ and $L_g = 160\ \mu H$                                                                                                                                      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPQC                        | DC link capacitors, $C_{dc} = 1100  \mu\text{F}$<br>Reference DC link voltage = 230 V<br>Series filter, $L_{sr} = 2.5  \text{mH}  C_{sr} = 15  \mu\text{F}$<br>Shunt filter, $L_{sh} = 5  \text{mH}$<br>Series transformer = 240/240 V (1:1 ratio) |

| Load                        | Linear: $R = 27 \Omega$ and $L = 50 \text{ mH}$<br>Non Linear $R = 57 \Omega$ and $L = 5 \text{ mH}$<br>Nominal Load voltage $V_{L-L peak} = 50 \text{V}$                                                                                          |

Fig. 8. Experimental result: power factor correction during steady state condition.

Fig. 8 depicts the steady state performance of the proposed ten-switch UPQC system considering a linear RL load ( $|V_{pcc}| = 1 \ p.u$ ). Initially, the shunt VSI is maintaining the dc-link voltage by drawing a small current (Fig. 8(c)), whereas, the load reactive power is supplied by the grid. As seen from Fig 8(e), the grid current lags the grid voltage by  $37^{\circ}$ . The reactive compensation starts at time t = T. The shunt VSI injects the necessary current causing the grid to supply only the load active power (i.e. grid current being inphase with the grid voltage as shown in Fig. 8(e)).

On the same system, a sudden sag condition is imposed. An unbalance voltage sag is introduced in the grid voltage as shown in Fig. 9(a). It can be seen from Fig. 9 that the proposed ten-switch UPQC effectively maintains the dc link as well as the load voltage at nominal values (Figs. 9(b) and (c)). The series controller injects the missing component inphase with the positive sequence voltage and cancels the negative sequence component of PCC voltage. Further, the performance of proposed UPQC configuration is validated under worst case scenario of maximum three-phase balanced voltage sag depth of 40% with only non-linear load (diode bridge rectifier with current THD of 28%) connected to the system. As shown in Fig. 10 (c), the load voltage are maintained at rated value in this case as well. Additionally, the shunt-VSI compensates the harmonics in the load current and maintains the dc-link voltage at reference value. The source current THD is improved from 28% to 1.8%.

Fig. 11 depicts the performance of proposed ten-switch UPQC when the PCC voltage and load current are distorted. A

combination of linear (RL) and nonlinear load is considered with the combined load current THD of 18%. The 5<sup>th</sup> and 7<sup>th</sup> harmonic voltages are added in the grid voltage to achieve a THD of 10%.

Fig.9. Experimental result: transition from steady state to unbalanced voltage sag condition (with liner RL load).

Fig.10. Experimental result: transition from steady state to balanced voltage sag condition (with non-linear load).

Fig. 11. Experimental result: distorted supply and unbalanced nonlinear load condition

The series part effectively mitigates the harmonics in the grid voltage. The improved load voltage profile can be noticed from Fig. 11(d) wherein the THD is reduced to 3%. Simultaneously, the shunt controller effectively compensates the load current harmonics achieving sinusoidal grid currents with the THD of 2.1%. Thus, the above experimental study verifies the feasibility of the proposed ten-switch UPQC topology for practical applications to improve the power quality.

#### VIII. CONCLUSION

To overcome the limitations of nine-switch based reduced switch power conditioner, this paper proposes a new structure of UPQC using ten semiconductor switches. The salient feature of the proposed topology is its capability of maintaining the same power quality enhancement with less number of switches and without increasing the switch VA rating. A comparative study is conducted and the results demonstrate that the proposed ten-switch topology can achieve the same power quality mitigation performance with the least VA loading of the UPQC system. The performance of the proposed topology has been validated experimentally under various operating conditions.

#### REFERENCES

- [1] R. C. Dugan, M. F. McGranaghan, and H. W. Beaty, *Electrical Power Systems Quality*.. New York: McGraw-Hill, 1996, p. 265.

- [2] B. Han, B. Bae, H. Kim, and S. Baek, "Combined operation of unified power-quality conditioner with distributed generation," *IEEE Trans. Power Delivery*, vol. 21, no. 1, pp. 330–338, Jan. 2006.

- [3] IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems," *IEEE Std 519-1992*, vol., no., pp.1,112, April 9 1993.

- [4] V. Khadkikar, "Enhancing electric power quality using UPQC: A comprehensive overview," *IEEE Trans. Power Electron.*, vol. 27, no. 5, pp.2284–2297, May 2012.

- [5] H. Fujita and H. Akagi, "The unified power quality conditioner: The integration of series- and shunt-active filters," *IEEE Trans. Power Electron.*, vol. 13, no. 2, pp. 315–322, Mar. 1998.

- [6] H. R. Mohammadi, R. Y. Varjani, and H. Mokhtari, "Multiconverter unified power-quality conditioning system: MC-UPQC," *IEEE Trans. Power Del.*, vol. 24, no. 3, pp. 1679–1686, Jul. 2009.

- [7] V. Khadkikar and A. Chandra, "UPQC-S: A novel concept of simultaneous voltage sag/swell and load reactive power compensations utilizing series inverter of UPQC," *IEEE Trans. Power Electron.*, vol. 26, no. 9, pp. 2414–2425, Sep. 2011.

- [8] V. Khadkikar and A. Chandra, "A novel structure for three-phase four wire distribution system utilizing unified power quality conditioner (UPQC)," *IEEE Trans. Ind. Appl.*, vol. 45, no. 5, pp. 1897–1902, Sep./Oct. 2009.

- [9] M. Basu, S. P. Das, and G. K. Dubey, "Comparative evaluation of two models of UPQC for suitable interface to enhance power quality," *Elect. Power Syst. Res.*, vol. 77, pp. 821–830, 2007.

- [10] Y. Li, D. M. Vilathgamuwa, and P. C. Loh, "Microgrid power quality enhancement using a three-phase four-wire grid-interfacing compensator," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1707–1719, Nov./Dec. 2005.

- [11] M. J. Newman, D. G. Holmes, J. G. Nielsen, and F. Blaabjerg, "A dynamic voltage restorer (DVR) with selective harmonic compensation at medium voltage level," *IEEE Trans. Ind. Applicat.*, vol. 41, no. 6, pp. 1744–1753, Nov./Dec. 2005.

- [12] M. J. Newman and D. G. Holmes, "A universal custom power conditioner (UCPC) with selective harmonic voltage compensation," in Proc. IEEE-IECON, 2002, pp. 1261–1266.

- [13] L. Zhang, P. C. Loh, and F. Gao, "An integrated nine-switch power conditioner for power quality enhancement and voltage sag mitigation," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1177–1190, Mar. 2011.

- [14] P. Delarue, A. Bouscayrol and B. Francois, "Control implementation of a five-leg voltage-source-inverter supplying two three-phase induction machines," in Proc. IEEE IEMDC, Madison, WI, 2003, pp. 1909–1915.

- [15] S. N. Vukosavic, M. Jones, D. Dujic, and E. Levi, "An improved PWM method for a five-leg inverter supplying two three-phase motors," in Proc. IEEE ISIE, Cambridge, U.K., 2008, pp. 160–165.

- [16] C. B. Jacobina, E. C. dos Santos, Jr., E. R. C. da Silva, M. B. de R. Correa, A. M. N. Lima, and T. M. Oliveira, "Reduced switch count multiple three-phase AC machine drive systems," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 966–976, Mar. 2008.

- [17] B. Francois and A. Bouscayrol, "Design and modeling of a five-phase voltage-source inverter for two induction motors," in Proc. EPE Appl. Conf., Lausanne, Switzerland, 1999. CD-ROM.

- [18] R. Omata, K. Oka, A. Furuya, S. Matsumoto, Y. Nozawa, and K. Matsuse, "An improved performance of five-leg inverter in two induction motor drives," in Proc. CES/IEEE 5th Int. Power Electron. Motion Control Conf., 2006, pp. 1–5.

- [19] M. Jones, D. Dujic, E. Levi, M. Bebic, and B. Jeftenic, "A two-motor centre driven winder fed by a five-leg voltage source inverter," in Proc. Eur. Conf. Power Electron. Appl., 2007, pp. 1–10.

- [20] M. Jones, S. N. Vukosavic, D. Dujic, E. Levi, and P. Wright, "Tenswitch inverter PWM technique for reduced switch count two-motor constant power applications," *IET Proc. Electric Power Applicat.*, vol. 2, no. 5, pp. 275–287, Sep. 2008.

- [21] P. Delarue, A. Bouscayrol, and E. Semail, "Generic control method of multileg voltage-source-converters for fast practical implementation," *IEEE Trans. Power Electron.*, vol. 18, no. 2, pp. 517–526, Mar. 2003.

- [22] P. C. Loh, A. S. Bahman, Z. Qin and F. Blaabjerg, "Loss comparison of different nine-switch and twelve-switch energy conversion systems," in Proc. IEEE-APEC, 2014, pp. 309-314.

- [23] P. C. Loh, A. S. Bahman, Z. Qin and F. Blaabjerg, "Evaluation of Switch Currents in Nine-Switch Energy Conversion Systems," in Proc IEEE-IECON'13, 2013, pp. 753-758.

- [24] K. Oka, Y. Nozawa, and R. Omata, "Characteristic comparison between five-leg inverter and nine-switch inverter," in Proc. Power Convers. Conf.,, Nagoya, Japan, 2007, pp. 279–283.

Abdul Mannan Rauf received the B.Sc. degree in electrical engineering from University of Engineering and Technology (UET) Taxila, Pakistan, in 2009 and the M.Sc. degree in electrical power engineering from Masdar Institute of Science and Technology, Abu Dhabi, UAE, in 2014. Since August 2014 he has been working as a Research Engineer at Masdar Institute of Science and Technology, Abu Dhabi, UAE.

From 2010 to 2012, he was with DTS (subcon:TRANSCO) Abu Dhabi UAE as a Project Engineer for Medium and High Voltage Substations. His research interests include FACTS devices, power quality enhancement in distribution systems and high power electronic converter

Amit Vilas Sant received his Ph.D. in Electrical Engineering from the Indian Institute of Technology Delhi, New Delhi, India in 2013. Prior to that, he obtained his Master of Technology degree in Electrical Engineering and Bachelor of Engineering (Electrical and Electronics) from Nirma University, Ahmedabad, India and Manipal University, Manipal, India, respectively. During his Master's he was awarded the Best Student Award and Gold

Medal for scholastic achievements. From April 2012 to September 2014, he was a Postdoctoral Researcher at the Masdar Institute of Science and Technology, Abu Dhabi, United Arab Emirates. Currently he is an Assistant Professor at BITS edu campus, Vadodara, India. His research interests include power electronics, electric drives, electric vehicles, multi-level inverters, photovoltaic systems, active power filters and power quality enhancement.

Vinod Khadkikar (S'06-M'09-SM'15) received his B.E. from the Government College of Engineering, Dr. Babasaheb Ambedkar Marathwada University, Aurangabad, India, in 2000, M. Tech. from the Indian Institute of Technology (IITD), New Delhi, India, in 2002 and Ph.D. degrees in Electrical Engineering from the École de Technologie Supérieure (E.T.S.), Montréal, QC, Canada, in 2008, all in Electrical Engineering.

From December 2008 to March 2010, he was a Postdoctoral Fellow at the University of Western Ontario, London, ON, Canada. From April 2010 to December 2010, he was a visiting faculty at Massachusetts Institute of Technology, Cambridge, MA, USA. Currently he is an Associate Professor at Masdar Institute of Science and Technology, Abu Dhabi, UAE. His research interests include applications of power electronics in distribution systems and renewable energy resources, grid interconnection issues, power quality enhancement, active power filters and electric vehicles. Dr. Khadkikar is currently an Associate Editor of the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS and IET POWER ELECTRONICS.

H. H. Zeineldin (M'06–SM'13) received the B.Sc. and M.Sc. degrees in electrical engineering from Cairo University, Cairo, Egypt, and the Ph.D. degree in electrical and computer engineering from the University of Waterloo, Waterloo, ON, Canada, in 2006. He was with Smith and Andersen Electrical Engineering, Inc., North York, ON, Canada, where he was involved with projects involving distribution system design, protection,

and distributed generation. He was then a Visiting Professor at the Massachusetts Institute of Technology, Cambridge, MA, USA. He is with the Faculty of Engineering, Cairo University, and currently he is a Professor with the Masdar Institute of Science and Technology, Abu Dhabi, UAE. His research interests include power system protection, distributed generation, and power system optimization. He is currently an Editor for the IEEE TRANSACTIONS ON ENERGY CONVERSION and the IEEE TRANSACTIONS ON SMART GRIDS.